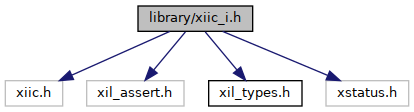

Include dependency graph for xiic_i.h:

Go to the source code of this file.

Macros | |

| #define | XIIC_I_H /* by using protection macros */ |

| #define | XIic_Send10BitAddrByte1(SlaveAddress, Operation) |

| #define | XIic_Send10BitAddrByte2(SlaveAddress) |

| #define | XIic_Send7BitAddr(SlaveAddress, Operation) |

| #define | XIic_DisableIntr(BaseAddress, InterruptMask) XIic_WriteIier((BaseAddress), XIic_ReadIier(BaseAddress) & ~(InterruptMask)) |

| #define | XIic_EnableIntr(BaseAddress, InterruptMask) XIic_WriteIier((BaseAddress), XIic_ReadIier(BaseAddress) | (InterruptMask)) |

| #define | XIic_ClearIntr(BaseAddress, InterruptMask) XIic_WriteIisr((BaseAddress), XIic_ReadIisr(BaseAddress) & (InterruptMask)) |

| #define | XIic_ClearEnableIntr(BaseAddress, InterruptMask) |

| #define | XIic_FlushRxFifo(InstancePtr) |

| #define | XIic_FlushTxFifo(InstancePtr) |

| #define | XIic_ReadRecvByte(InstancePtr) |

| #define | XIic_WriteSendByte(InstancePtr) |

| #define | XIic_SetControlRegister(InstancePtr, ControlRegister, ByteCount) |

Functions | |

| void | XIic_TransmitFifoFill (XIic *InstancePtr, int Role) |

Variables | |

| XIic_Config | XIic_ConfigTable [] |

| void(* | XIic_AddrAsSlaveFuncPtr )(XIic *InstancePtr) |

| void(* | XIic_NotAddrAsSlaveFuncPtr )(XIic *InstancePtr) |

| void(* | XIic_RecvSlaveFuncPtr )(XIic *InstancePtr) |

| void(* | XIic_SendSlaveFuncPtr )(XIic *InstancePtr) |

| void(* | XIic_RecvMasterFuncPtr )(XIic *InstancePtr) |

| void(* | XIic_SendMasterFuncPtr )(XIic *InstancePtr) |

| void(* | XIic_ArbLostFuncPtr )(XIic *InstancePtr) |

| void(* | XIic_BusNotBusyFuncPtr )(XIic *InstancePtr) |

Macro Definition Documentation

◆ XIic_ClearEnableIntr

| #define XIic_ClearEnableIntr | ( | BaseAddress, | |

| InterruptMask | |||

| ) |

Value:

{ \

XIic_WriteIisr(BaseAddress, \

(XIic_ReadIisr(BaseAddress) & (InterruptMask))); \

XIic_WriteIier(BaseAddress, \

(XIic_ReadIier(BaseAddress) | (InterruptMask))); \

}

◆ XIic_ClearIntr

| #define XIic_ClearIntr | ( | BaseAddress, | |

| InterruptMask | |||

| ) | XIic_WriteIisr((BaseAddress), XIic_ReadIisr(BaseAddress) & (InterruptMask)) |

◆ XIic_DisableIntr

| #define XIic_DisableIntr | ( | BaseAddress, | |

| InterruptMask | |||

| ) | XIic_WriteIier((BaseAddress), XIic_ReadIier(BaseAddress) & ~(InterruptMask)) |

◆ XIic_EnableIntr

| #define XIic_EnableIntr | ( | BaseAddress, | |

| InterruptMask | |||

| ) | XIic_WriteIier((BaseAddress), XIic_ReadIier(BaseAddress) | (InterruptMask)) |

◆ XIic_FlushRxFifo

| #define XIic_FlushRxFifo | ( | InstancePtr | ) |

Value:

{ \

int LoopCnt; \

u8 BytesToRead = \

XIic_ReadReg(InstancePtr->BaseAddress, XIIC_RFO_REG_OFFSET) + 1; \

for (LoopCnt = 0; LoopCnt < BytesToRead; LoopCnt++) { \

XIic_ReadReg(InstancePtr->BaseAddress, XIIC_DRR_REG_OFFSET); \

} \

}

◆ XIic_FlushTxFifo

| #define XIic_FlushTxFifo | ( | InstancePtr | ) |

Value:

; \

{ \

u32 CntlReg = XIic_ReadReg(InstancePtr->BaseAddress, XIIC_CR_REG_OFFSET); \

XIic_WriteReg(InstancePtr->BaseAddress, XIIC_CR_REG_OFFSET, \

CntlReg | XIIC_CR_TX_FIFO_RESET_MASK); \

XIic_WriteReg(InstancePtr->BaseAddress, XIIC_CR_REG_OFFSET, CntlReg); \

}

◆ XIIC_I_H

| #define XIIC_I_H /* by using protection macros */ |

This header file contains internal identifiers, which are those shared between XIic components. The identifiers in this file are not intended for use external to the driver.

MODIFICATION HISTORY:

Ver Who Date Changes

----- ---- -------- -----------------------------------------------

1.01a rfp 10/19/01 release

1.01c ecm 12/05/02 new rev

1.13a wgr 03/22/07 Converted to new coding style.

2.00a sdm 10/22/09 Converted all register accesses to 32 bit access.

Removed the macro XIIC_CLEAR_STATS, user has to

use the the XIic_ClearStats API in its place.

Removed the macro XIic_mEnterCriticalRegion,

XIic_IntrGlobalDisable should be used in its place.

Removed the macro XIic_mExitCriticalRegion,

XIic_IntrGlobalEnable should be used in its place.

Removed the _m prefix from all the macros

XIic_mSend10BitAddrByte1 is now XIic_Send10BitAddrByte1

XIic_mSend10BitAddrByte2 is now XIic_Send10BitAddrByte2

XIic_mSend7BitAddr is now XIic_Send7BitAddr

XIic_mDisableIntr is now XIic_DisableIntr

XIic_mEnableIntr is now XIic_EnableIntr

XIic_mClearIntr is now XIic_ClearIntr

XIic_mClearEnableIntr is now XIic_ClearEnableIntr

XIic_mFlushRxFifo is now XIic_FlushRxFifo

XIic_mFlushTxFifo is now XIic_FlushTxFifo

XIic_mReadRecvByte is now XIic_ReadRecvByte

XIic_mWriteSendByte is now XIic_WriteSendByte

XIic_mSetControlRegister is now XIic_SetControlRegister

2.07a adk 18/04/13 Updated the code to avoid unused variable warnings when

compiling with the -Wextra -Wall flags.

Changes done in files xiic.c and xiic_i.h. CR:705001

◆ XIic_ReadRecvByte

| #define XIic_ReadRecvByte | ( | InstancePtr | ) |

Value:

{ \

*InstancePtr->RecvBufferPtr++ = \

XIic_ReadReg(InstancePtr->BaseAddress, XIIC_DRR_REG_OFFSET); \

InstancePtr->RecvByteCount--; \

InstancePtr->Stats.RecvBytes++; \

}

◆ XIic_Send10BitAddrByte1

| #define XIic_Send10BitAddrByte1 | ( | SlaveAddress, | |

| Operation | |||

| ) |

Value:

{ \

u8 LocalAddr = (u8)((SlaveAddress) >> 7); \

LocalAddr = (LocalAddr & 0xF6) | 0xF0 | (Operation); \

XIic_WriteReg(InstancePtr->BaseAddress, XIIC_DTR_REG_OFFSET, \

(u32)LocalAddr); \

}

◆ XIic_Send10BitAddrByte2

| #define XIic_Send10BitAddrByte2 | ( | SlaveAddress | ) |

Value:

XIic_WriteReg(InstancePtr->BaseAddress, XIIC_DTR_REG_OFFSET, \

(u32)(SlaveAddress));

◆ XIic_Send7BitAddr

| #define XIic_Send7BitAddr | ( | SlaveAddress, | |

| Operation | |||

| ) |

Value:

{ \

u8 LocalAddr = (u8)(SlaveAddress << 1); \

LocalAddr = (LocalAddr & 0xFE) | (Operation); \

XIic_WriteReg(InstancePtr->BaseAddress, XIIC_DTR_REG_OFFSET, \

(u32)LocalAddr); \

}

◆ XIic_SetControlRegister

| #define XIic_SetControlRegister | ( | InstancePtr, | |

| ControlRegister, | |||

| ByteCount | |||

| ) |

Value:

{ \

(ControlRegister) &= ~(XIIC_CR_NO_ACK_MASK | XIIC_CR_DIR_IS_TX_MASK); \

if (InstancePtr->Options & XII_SEND_10_BIT_OPTION) { \

(ControlRegister) |= XIIC_CR_DIR_IS_TX_MASK; \

} else { \

if ((ByteCount) == 1) { \

(ControlRegister) |= XIIC_CR_NO_ACK_MASK; \

} \

} \

}

◆ XIic_WriteSendByte

| #define XIic_WriteSendByte | ( | InstancePtr | ) |

Value:

{ \

XIic_WriteReg(InstancePtr->BaseAddress, XIIC_DTR_REG_OFFSET, \

*InstancePtr->SendBufferPtr++); \

InstancePtr->SendByteCount--; \

InstancePtr->Stats.SendBytes++; \

}

Function Documentation

◆ XIic_TransmitFifoFill()

| void XIic_TransmitFifoFill | ( | XIic * | InstancePtr, |

| int | Role | ||

| ) |

Variable Documentation

◆ XIic_AddrAsSlaveFuncPtr

| void(* XIic_AddrAsSlaveFuncPtr) (XIic *InstancePtr) |

◆ XIic_ArbLostFuncPtr

| void(* XIic_ArbLostFuncPtr) (XIic *InstancePtr) |

◆ XIic_BusNotBusyFuncPtr

| void(* XIic_BusNotBusyFuncPtr) (XIic *InstancePtr) |

◆ XIic_ConfigTable

| XIic_Config XIic_ConfigTable[] |

◆ XIic_NotAddrAsSlaveFuncPtr

| void(* XIic_NotAddrAsSlaveFuncPtr) (XIic *InstancePtr) |

◆ XIic_RecvMasterFuncPtr

| void(* XIic_RecvMasterFuncPtr) (XIic *InstancePtr) |

◆ XIic_RecvSlaveFuncPtr

| void(* XIic_RecvSlaveFuncPtr) (XIic *InstancePtr) |

◆ XIic_SendMasterFuncPtr

| void(* XIic_SendMasterFuncPtr) (XIic *InstancePtr) |

◆ XIic_SendSlaveFuncPtr

| void(* XIic_SendSlaveFuncPtr) (XIic *InstancePtr) |