Go to the source code of this file.

Macros | |

| #define | XIIC_L_H /* by using protection macros */ |

Register Map | |

Register offsets for the XIic device. | |

| #define | XIIC_DGIER_OFFSET 0x1C |

| #define | XIIC_IISR_OFFSET 0x20 |

| #define | XIIC_IIER_OFFSET 0x28 |

| #define | XIIC_RESETR_OFFSET 0x40 |

| #define | XIIC_CR_REG_OFFSET 0x100 |

| #define | XIIC_SR_REG_OFFSET 0x104 |

| #define | XIIC_DTR_REG_OFFSET 0x108 |

| #define | XIIC_DRR_REG_OFFSET 0x10C |

| #define | XIIC_ADR_REG_OFFSET 0x110 |

| #define | XIIC_TFO_REG_OFFSET 0x114 |

| #define | XIIC_RFO_REG_OFFSET 0x118 |

| #define | XIIC_TBA_REG_OFFSET 0x11C |

| #define | XIIC_RFD_REG_OFFSET 0x120 |

| #define | XIIC_GPO_REG_OFFSET 0x124 |

Device Global Interrupt Enable Register masks (CR) mask(s) | |

| #define | XIIC_GINTR_ENABLE_MASK 0x80000000 |

IIC Device Interrupt Status/Enable (INTR) Register Masks | |

Interrupt Status Register (IISR) This register holds the interrupt status flags for the Spi device. Interrupt Enable Register (IIER) This register is used to enable interrupt sources for the IIC device. Writing a '1' to a bit in this register enables the corresponding Interrupt. Writing a '0' to a bit in this register disables the corresponding Interrupt. IISR/IIER registers have the same bit definitions and are only defined once. | |

| #define | XIIC_INTR_ARB_LOST_MASK 0x00000001 |

| #define | XIIC_INTR_TX_ERROR_MASK 0x00000002 |

| #define | XIIC_INTR_TX_EMPTY_MASK 0x00000004 |

| #define | XIIC_INTR_RX_FULL_MASK 0x00000008 |

| #define | XIIC_INTR_BNB_MASK 0x00000010 |

| #define | XIIC_INTR_AAS_MASK 0x00000020 |

| #define | XIIC_INTR_NAAS_MASK 0x00000040 |

| #define | XIIC_INTR_TX_HALF_MASK 0x00000080 |

| #define | XIIC_TX_INTERRUPTS (XIIC_INTR_TX_ERROR_MASK | XIIC_INTR_TX_EMPTY_MASK | XIIC_INTR_TX_HALF_MASK) |

| #define | XIIC_TX_RX_INTERRUPTS (XIIC_INTR_RX_FULL_MASK | XIIC_TX_INTERRUPTS) |

Reset Register mask | |

| #define | XIIC_RESET_MASK 0x0000000A |

Control Register masks (CR) mask(s) | |

| #define | XIIC_CR_ENABLE_DEVICE_MASK 0x00000001 |

| #define | XIIC_CR_TX_FIFO_RESET_MASK 0x00000002 |

| #define | XIIC_CR_MSMS_MASK 0x00000004 |

| #define | XIIC_CR_DIR_IS_TX_MASK 0x00000008 |

| #define | XIIC_CR_NO_ACK_MASK 0x00000010 |

| #define | XIIC_CR_REPEATED_START_MASK 0x00000020 |

| #define | XIIC_CR_GENERAL_CALL_MASK 0x00000040 |

Status Register masks (SR) mask(s) | |

| #define | XIIC_SR_GEN_CALL_MASK 0x00000001 |

| #define | XIIC_SR_ADDR_AS_SLAVE_MASK 0x00000002 |

| #define | XIIC_SR_BUS_BUSY_MASK 0x00000004 |

| #define | XIIC_SR_MSTR_RDING_SLAVE_MASK 0x00000008 |

| #define | XIIC_SR_TX_FIFO_FULL_MASK 0x00000010 |

| #define | XIIC_SR_RX_FIFO_FULL_MASK 0x00000020 |

| #define | XIIC_SR_RX_FIFO_EMPTY_MASK 0x00000040 |

| #define | XIIC_SR_TX_FIFO_EMPTY_MASK 0x00000080 |

Data Tx Register (DTR) mask(s) | |

| #define | XIIC_TX_DYN_START_MASK 0x00000100 |

| #define | XIIC_TX_DYN_STOP_MASK 0x00000200 |

| #define | IIC_TX_FIFO_DEPTH 16 |

Data Rx Register (DRR) mask(s) | |

| #define | IIC_RX_FIFO_DEPTH 16 |

| #define | XIIC_TX_ADDR_SENT 0x00 |

| #define | XIIC_TX_ADDR_MSTR_RECV_MASK 0x02 |

| #define | XIIC_READ_OPERATION 1 |

| #define | XIIC_WRITE_OPERATION 0 |

| #define | XIIC_MASTER_ROLE 1 |

| #define | XIIC_SLAVE_ROLE 0 |

| #define | XIIC_STOP 0x00 |

| #define | XIIC_REPEATED_START 0x01 |

| #define | XIic_In32 Xil_In32 |

| #define | XIic_Out32 Xil_Out32 |

| #define | XIic_ReadReg(BaseAddress, RegOffset) XIic_In32((BaseAddress) + (RegOffset)) |

| #define | XIic_WriteReg(BaseAddress, RegOffset, RegisterValue) XIic_Out32((BaseAddress) + (RegOffset), (RegisterValue)) |

| #define | XIic_IntrGlobalDisable(BaseAddress) XIic_WriteReg((BaseAddress), XIIC_DGIER_OFFSET, 0) |

| #define | XIic_IntrGlobalEnable(BaseAddress) XIic_WriteReg((BaseAddress), XIIC_DGIER_OFFSET, XIIC_GINTR_ENABLE_MASK) |

| #define | XIic_IsIntrGlobalEnabled(BaseAddress) (XIic_ReadReg((BaseAddress), XIIC_DGIER_OFFSET) == XIIC_GINTR_ENABLE_MASK) |

| #define | XIic_WriteIisr(BaseAddress, Status) XIic_WriteReg((BaseAddress), XIIC_IISR_OFFSET, (Status)) |

| #define | XIic_ReadIisr(BaseAddress) XIic_ReadReg((BaseAddress), XIIC_IISR_OFFSET) |

| #define | XIic_WriteIier(BaseAddress, Enable) XIic_WriteReg((BaseAddress), XIIC_IIER_OFFSET, (Enable)) |

| #define | XIic_ReadIier(BaseAddress) XIic_ReadReg((BaseAddress), XIIC_IIER_OFFSET) |

| #define | XIic_ClearIisr(BaseAddress, InterruptMask) XIic_WriteIisr((BaseAddress), XIic_ReadIisr(BaseAddress) & (InterruptMask)) |

| #define | XIic_Send7BitAddress(BaseAddress, SlaveAddress, Operation) |

| #define | XIic_DynSend7BitAddress(BaseAddress, SlaveAddress, Operation) |

| #define | XIic_DynSendStartStopAddress(BaseAddress, SlaveAddress, Operation) |

| #define | XIic_DynSendStop(BaseAddress, ByteCount) |

| unsigned | XIic_Recv (UINTPTR BaseAddress, u8 Address, u8 *BufferPtr, unsigned ByteCount, u8 Option) |

| unsigned | XIic_Send (UINTPTR BaseAddress, u8 Address, u8 *BufferPtr, unsigned ByteCount, u8 Option) |

| unsigned | XIic_DynRecv (UINTPTR BaseAddress, u8 Address, u8 *BufferPtr, u8 ByteCount) |

| unsigned | XIic_DynSend (UINTPTR BaseAddress, u16 Address, u8 *BufferPtr, u8 ByteCount, u8 Option) |

| int | XIic_DynInit (UINTPTR BaseAddress) |

| u32 | XIic_CheckIsBusBusy (UINTPTR BaseAddress) |

| u32 | XIic_WaitBusFree (UINTPTR BaseAddress) |

Macro Definition Documentation

◆ IIC_RX_FIFO_DEPTH

◆ IIC_TX_FIFO_DEPTH

◆ XIIC_ADR_REG_OFFSET

◆ XIic_ClearIisr

| #define XIic_ClearIisr | ( | BaseAddress, | |

| InterruptMask | |||

| ) | XIic_WriteIisr((BaseAddress), XIic_ReadIisr(BaseAddress) & (InterruptMask)) |

This macro clears the specified interrupt in the Interrupt status register. It is non-destructive in that the register is read and only the interrupt specified is cleared. Clearing an interrupt acknowledges it.

- Parameters

-

BaseAddress is the base address of the IIC device. InterruptMask is the bit mask of the interrupts to be cleared.

- Returns

- None.

- Note

- C-Style signature: void XIic_ClearIisr(u32 BaseAddress, u32 InterruptMask);

◆ XIIC_CR_DIR_IS_TX_MASK

| #define XIIC_CR_DIR_IS_TX_MASK 0x00000008 |

◆ XIIC_CR_ENABLE_DEVICE_MASK

| #define XIIC_CR_ENABLE_DEVICE_MASK 0x00000001 |

◆ XIIC_CR_GENERAL_CALL_MASK

| #define XIIC_CR_GENERAL_CALL_MASK 0x00000040 |

◆ XIIC_CR_MSMS_MASK

◆ XIIC_CR_NO_ACK_MASK

◆ XIIC_CR_REG_OFFSET

◆ XIIC_CR_REPEATED_START_MASK

| #define XIIC_CR_REPEATED_START_MASK 0x00000020 |

◆ XIIC_CR_TX_FIFO_RESET_MASK

| #define XIIC_CR_TX_FIFO_RESET_MASK 0x00000002 |

◆ XIIC_DGIER_OFFSET

| #define XIIC_DGIER_OFFSET 0x1C |

◆ XIIC_DRR_REG_OFFSET

◆ XIIC_DTR_REG_OFFSET

◆ XIic_DynSend7BitAddress

| #define XIic_DynSend7BitAddress | ( | BaseAddress, | |

| SlaveAddress, | |||

| Operation | |||

| ) |

This macro sends the address for a 7 bit address during both read and write operations. It takes care of the details to format the address correctly. This macro is designed to be called internally to the drivers for Dynamic controller functionality.

- Parameters

-

BaseAddress is the base address of the IIC Device. SlaveAddress is the address of the slave to send to. Operation indicates XIIC_READ_OPERATION or XIIC_WRITE_OPERATION.

- Returns

- None.

- Note

- C-Style signature: void XIic_DynSend7BitAddress(u32 BaseAddress, u8 SlaveAddress, u8 Operation);

◆ XIic_DynSendStartStopAddress

| #define XIic_DynSendStartStopAddress | ( | BaseAddress, | |

| SlaveAddress, | |||

| Operation | |||

| ) |

This macro sends the address, start and stop for a 7 bit address during both write operations. It takes care of the details to format the address correctly. This macro is designed to be called internally to the drivers.

- Parameters

-

BaseAddress is the base address of the IIC Device. SlaveAddress is the address of the slave to send to. Operation indicates XIIC_WRITE_OPERATION.

- Returns

- None.

- Note

- C-Style signature: void XIic_DynSendStartStopAddress(u32 BaseAddress, u8 SlaveAddress, u8 Operation);

◆ XIic_DynSendStop

| #define XIic_DynSendStop | ( | BaseAddress, | |

| ByteCount | |||

| ) |

This macro sends a stop condition on IIC bus for Dynamic logic.

- Parameters

-

BaseAddress is the base address of the IIC Device. ByteCount is the number of Rx bytes received before the master. doesn't respond with ACK.

- Returns

- None.

- Note

- C-Style signature: void XIic_DynSendStop(u32 BaseAddress, u32 ByteCount);

◆ XIIC_GINTR_ENABLE_MASK

| #define XIIC_GINTR_ENABLE_MASK 0x80000000 |

◆ XIIC_GPO_REG_OFFSET

◆ XIIC_IIER_OFFSET

◆ XIIC_IISR_OFFSET

◆ XIic_In32

◆ XIIC_INTR_AAS_MASK

| #define XIIC_INTR_AAS_MASK 0x00000020 |

◆ XIIC_INTR_ARB_LOST_MASK

| #define XIIC_INTR_ARB_LOST_MASK 0x00000001 |

◆ XIIC_INTR_BNB_MASK

◆ XIIC_INTR_NAAS_MASK

| #define XIIC_INTR_NAAS_MASK 0x00000040 |

◆ XIIC_INTR_RX_FULL_MASK

| #define XIIC_INTR_RX_FULL_MASK 0x00000008 |

◆ XIIC_INTR_TX_EMPTY_MASK

| #define XIIC_INTR_TX_EMPTY_MASK 0x00000004 |

◆ XIIC_INTR_TX_ERROR_MASK

| #define XIIC_INTR_TX_ERROR_MASK 0x00000002 |

◆ XIIC_INTR_TX_HALF_MASK

| #define XIIC_INTR_TX_HALF_MASK 0x00000080 |

◆ XIic_IntrGlobalDisable

| #define XIic_IntrGlobalDisable | ( | BaseAddress | ) | XIic_WriteReg((BaseAddress), XIIC_DGIER_OFFSET, 0) |

This macro disables all interrupts for the device by writing to the Global interrupt enable register.

- Parameters

-

BaseAddress is the base address of the IIC device.

- Returns

- None.

- Note

- C-Style signature: void XIic_IntrGlobalDisable(u32 BaseAddress);

◆ XIic_IntrGlobalEnable

| #define XIic_IntrGlobalEnable | ( | BaseAddress | ) | XIic_WriteReg((BaseAddress), XIIC_DGIER_OFFSET, XIIC_GINTR_ENABLE_MASK) |

This macro writes to the global interrupt enable register to enable interrupts from the device. This function does not enable individual interrupts as the Interrupt Enable Register must be set appropriately.

- Parameters

-

BaseAddress is the base address of the IIC device.

- Returns

- None.

- Note

- C-Style signature: void XIic_IntrGlobalEnable(u32 BaseAddress);

◆ XIic_IsIntrGlobalEnabled

| #define XIic_IsIntrGlobalEnabled | ( | BaseAddress | ) | (XIic_ReadReg((BaseAddress), XIIC_DGIER_OFFSET) == XIIC_GINTR_ENABLE_MASK) |

This function determines if interrupts are enabled at the global level by reading the global interrupt register.

- Parameters

-

BaseAddress is the base address of the IIC device.

- Returns

- TRUE if the global interrupt is enabled.

- FALSE if global interrupt is disabled.

- Note

- C-Style signature: int XIic_IsIntrGlobalEnabled(u32 BaseAddress);

◆ XIIC_L_H

| #define XIIC_L_H /* by using protection macros */ |

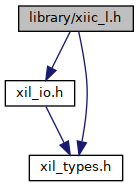

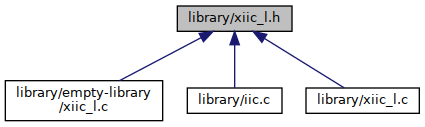

This header file contains identifiers and driver functions (or macros) that can be used to access the device in normal and dynamic controller mode. High-level driver functions are defined in xiic.h.

MODIFICATION HISTORY:

Ver Who Date Changes

----- ---- -------- -----------------------------------------------

1.00b jhl 05/07/02 First release

1.01c ecm 12/05/02 new rev

1.01d jhl 10/08/03 Added general purpose output feature

1.02a mta 03/09/06 Implemented Repeated Start in the Low Level Driver.

1.03a mta 04/04/06 Implemented Dynamic IIC core routines.

1.03a rpm 09/08/06 Added include of xstatus.h for completeness

1.13a wgr 03/22/07 Converted to new coding style.

1.16a ktn 07/18/09 Updated the notes in XIIC_RESET macro to clearly indicate

that only the Interrupt Registers are reset.

1.16a ktn 10/16/09 Updated the notes in the XIIC_RESET macro to mention

that the complete IIC core is Reset on giving a software

reset to the IIC core. Some previous versions of the

core only reset the Interrupt Logic/Registers, please

refer to the HW specification for further details.

2.00a sdm 10/22/09 Converted all register accesses to 32 bit access,

the register offsets are defined to be on 32 bit boundary.

Removed the macro XIIC_RESET, XIic_Reset API should be

used in its place.

Some of the macros have been renamed to be consistent -

XIIC_GINTR_DISABLE is renamed as XIic_IntrGlobalDisable,

XIIC_GINTR_ENABLE is renamed as XIic_IntrGlobalEnable,

XIIC_IS_GINTR_ENABLED is renamed as

XIic_IsIntrGlobalEnabled,

XIIC_WRITE_IISR is renamed as XIic_WriteIisr,

XIIC_READ_IISR is renamed as XIic_ReadIisr,

XIIC_WRITE_IIER is renamed as XIic_WriteIier

The _m prefix in the name of the macros has been removed -

XIic_mClearIisr is now XIic_ClearIisr,

XIic_mSend7BitAddress is now XIic_Send7BitAddress,

XIic_mDynSend7BitAddress is now XIic_DynSend7BitAddress,

XIic_mDynSendStartStopAddress is now

XIic_DynSendStartStopAddress,

XIic_mDynSendStop is now XIic_DynSendStop.

3.2 sk 11/10/15 Used UINTPTR instead of u32 for Baseaddress CR# 867425.

Changed the prototypes of XIic_Recv, XIic_Send,

XIic_DynRecv, XIic_DynSend and XIic_DynInit APIs.

3.3 als 06/27/16 Added Low-level XIic_CheckIsBusBusy API.

3.3 als 06/27/16 Added low-level XIic_WaitBusFree API.

◆ XIIC_MASTER_ROLE

| #define XIIC_MASTER_ROLE 1 |

◆ XIic_Out32

◆ XIIC_READ_OPERATION

| #define XIIC_READ_OPERATION 1 |

◆ XIic_ReadIier

| #define XIic_ReadIier | ( | BaseAddress | ) | XIic_ReadReg((BaseAddress), XIIC_IIER_OFFSET) |

This function gets the Interrupt Enable Register contents.

- Parameters

-

BaseAddress is the base address of the IIC device.

- Returns

- The contents read from the Interrupt Enable Register. Bit positions of 1 indicate that the corresponding interrupt is enabled. Bit positions of 0 indicate that the corresponding interrupt is disabled.

- Note

- C-Style signature: u32 XIic_ReadIier(u32 BaseAddress)

◆ XIic_ReadIisr

| #define XIic_ReadIisr | ( | BaseAddress | ) | XIic_ReadReg((BaseAddress), XIIC_IISR_OFFSET) |

This function gets the contents of the Interrupt Status Register. This register indicates the status of interrupt sources for the device. The status is independent of whether interrupts are enabled such that the status register may also be polled when interrupts are not enabled.

- Parameters

-

BaseAddress is the base address of the IIC device.

- Returns

- The value read from the Interrupt Status Register.

- Note

- C-Style signature: u32 XIic_ReadIisr(u32 BaseAddress);

◆ XIic_ReadReg

| #define XIic_ReadReg | ( | BaseAddress, | |

| RegOffset | |||

| ) | XIic_In32((BaseAddress) + (RegOffset)) |

Read from the specified IIC device register.

- Parameters

-

BaseAddress is the base address of the device. RegOffset is the offset from the 1st register of the device to select the specific register.

- Returns

- The value read from the register.

- Note

- C-Style signature: u32 XIic_ReadReg(u32 BaseAddress, u32 RegOffset);

This macro does not do any checking to ensure that the

register exists if the register may be excluded due to parameterization, such as the GPO Register.

◆ XIIC_REPEATED_START

| #define XIIC_REPEATED_START 0x01 |

◆ XIIC_RESET_MASK

◆ XIIC_RESETR_OFFSET

◆ XIIC_RFD_REG_OFFSET

◆ XIIC_RFO_REG_OFFSET

◆ XIic_Send7BitAddress

| #define XIic_Send7BitAddress | ( | BaseAddress, | |

| SlaveAddress, | |||

| Operation | |||

| ) |

This macro sends the address for a 7 bit address during both read and write operations. It takes care of the details to format the address correctly. This macro is designed to be called internally to the drivers.

- Parameters

-

BaseAddress is the base address of the IIC Device. SlaveAddress is the address of the slave to send to. Operation indicates XIIC_READ_OPERATION or XIIC_WRITE_OPERATION

- Returns

- None.

- Note

- C-Style signature: void XIic_Send7BitAddress(u32 BaseAddress, u8 SlaveAddress, u8 Operation);

◆ XIIC_SLAVE_ROLE

◆ XIIC_SR_ADDR_AS_SLAVE_MASK

| #define XIIC_SR_ADDR_AS_SLAVE_MASK 0x00000002 |

◆ XIIC_SR_BUS_BUSY_MASK

◆ XIIC_SR_GEN_CALL_MASK

| #define XIIC_SR_GEN_CALL_MASK 0x00000001 |

◆ XIIC_SR_MSTR_RDING_SLAVE_MASK

| #define XIIC_SR_MSTR_RDING_SLAVE_MASK 0x00000008 |

◆ XIIC_SR_REG_OFFSET

◆ XIIC_SR_RX_FIFO_EMPTY_MASK

| #define XIIC_SR_RX_FIFO_EMPTY_MASK 0x00000040 |

◆ XIIC_SR_RX_FIFO_FULL_MASK

| #define XIIC_SR_RX_FIFO_FULL_MASK 0x00000020 |

◆ XIIC_SR_TX_FIFO_EMPTY_MASK

| #define XIIC_SR_TX_FIFO_EMPTY_MASK 0x00000080 |

◆ XIIC_SR_TX_FIFO_FULL_MASK

| #define XIIC_SR_TX_FIFO_FULL_MASK 0x00000010 |

◆ XIIC_STOP

| #define XIIC_STOP 0x00 |

◆ XIIC_TBA_REG_OFFSET

◆ XIIC_TFO_REG_OFFSET

◆ XIIC_TX_ADDR_MSTR_RECV_MASK

◆ XIIC_TX_ADDR_SENT

◆ XIIC_TX_DYN_START_MASK

| #define XIIC_TX_DYN_START_MASK 0x00000100 |

◆ XIIC_TX_DYN_STOP_MASK

| #define XIIC_TX_DYN_STOP_MASK 0x00000200 |

◆ XIIC_TX_INTERRUPTS

| #define XIIC_TX_INTERRUPTS (XIIC_INTR_TX_ERROR_MASK | XIIC_INTR_TX_EMPTY_MASK | XIIC_INTR_TX_HALF_MASK) |

◆ XIIC_TX_RX_INTERRUPTS

| #define XIIC_TX_RX_INTERRUPTS (XIIC_INTR_RX_FULL_MASK | XIIC_TX_INTERRUPTS) |

◆ XIIC_WRITE_OPERATION

| #define XIIC_WRITE_OPERATION 0 |

◆ XIic_WriteIier

| #define XIic_WriteIier | ( | BaseAddress, | |

| Enable | |||

| ) | XIic_WriteReg((BaseAddress), XIIC_IIER_OFFSET, (Enable)) |

This function sets the contents of the Interrupt Enable Register.

This function writes only the specified value to the register such that some interrupt sources may be enabled and others disabled. It is the caller's responsibility to get the value of the interrupt enable register prior to setting the value to prevent a destructive behavior.

- Parameters

-

BaseAddress is the base address of the IIC device. Enable is the value to be written to the Interrupt Enable Register. Bit positions of 1 will be enabled. Bit positions of 0 will be disabled.

- Returns

- None

- Note

- C-Style signature: void XIic_WriteIier(u32 BaseAddress, u32 Enable);

◆ XIic_WriteIisr

| #define XIic_WriteIisr | ( | BaseAddress, | |

| Status | |||

| ) | XIic_WriteReg((BaseAddress), XIIC_IISR_OFFSET, (Status)) |

This function sets the Interrupt status register to the specified value.

This register implements a toggle on write functionality. The interrupt is cleared by writing to this register with the bits to be cleared set to a one and all others to zero. Setting a bit which is zero within this register causes an interrupt to be generated.

This function writes only the specified value to the register such that some status bits may be set and others cleared. It is the caller's responsibility to get the value of the register prior to setting the value to prevent an destructive behavior.

- Parameters

-

BaseAddress is the base address of the IIC device. Status is the value to be written to the Interrupt status register.

- Returns

- None.

- Note

- C-Style signature: void XIic_WriteIisr(u32 BaseAddress, u32 Status);

◆ XIic_WriteReg

| #define XIic_WriteReg | ( | BaseAddress, | |

| RegOffset, | |||

| RegisterValue | |||

| ) | XIic_Out32((BaseAddress) + (RegOffset), (RegisterValue)) |

Write to the specified IIC device register.

- Parameters

-

BaseAddress is the base address of the device. RegOffset is the offset from the 1st register of the device to select the specific register. RegisterValue is the value to be written to the register.

- Returns

- None.

- Note

- C-Style signature: void XIic_WriteReg(u32 BaseAddress, u32 RegOffset, u32 RegisterValue); This macro does not do any checking to ensure that the register exists if the register may be excluded due to parameterization, such as the GPO Register.

Function Documentation

◆ XIic_CheckIsBusBusy()

| u32 XIic_CheckIsBusBusy | ( | UINTPTR | BaseAddress | ) |

◆ XIic_DynInit()

◆ XIic_DynRecv()

| unsigned XIic_DynRecv | ( | UINTPTR | BaseAddress, |

| u8 | Address, | ||

| u8 * | BufferPtr, | ||

| u8 | ByteCount | ||

| ) |

◆ XIic_DynSend()

| unsigned XIic_DynSend | ( | UINTPTR | BaseAddress, |

| u16 | Address, | ||

| u8 * | BufferPtr, | ||

| u8 | ByteCount, | ||

| u8 | Option | ||

| ) |

◆ XIic_Recv()

| unsigned XIic_Recv | ( | UINTPTR | BaseAddress, |

| u8 | Address, | ||

| u8 * | BufferPtr, | ||

| unsigned | ByteCount, | ||

| u8 | Option | ||

| ) |

Receive data as a master on the IIC bus. This function receives the data using polled I/O and blocks until the data has been received. It only supports 7 bit addressing mode of operation. This function returns zero if bus is busy.

- Parameters

-

BaseAddress contains the base address of the IIC device. Address contains the 7 bit IIC address of the device to send the specified data to. BufferPtr points to the data to be sent. ByteCount is the number of bytes to be sent. Option indicates whether to hold or free the bus after reception of data, XIIC_STOP = end with STOP condition, XIIC_REPEATED_START = don't end with STOP condition.

- Returns

- The number of bytes received.

- Note

- None.

◆ XIic_Send()

| unsigned XIic_Send | ( | UINTPTR | BaseAddress, |

| u8 | Address, | ||

| u8 * | BufferPtr, | ||

| unsigned | ByteCount, | ||

| u8 | Option | ||

| ) |

Send data as a master on the IIC bus. This function sends the data using polled I/O and blocks until the data has been sent. It only supports 7 bit addressing mode of operation. This function returns zero if bus is busy.

- Parameters

-

BaseAddress contains the base address of the IIC device. Address contains the 7 bit IIC address of the device to send the specified data to. BufferPtr points to the data to be sent. ByteCount is the number of bytes to be sent. Option indicates whether to hold or free the bus after transmitting the data.

- Returns

- The number of bytes sent.

- Note

- None.

Definition at line 4 of file xiic_l.c.

◆ XIic_WaitBusFree()

| u32 XIic_WaitBusFree | ( | UINTPTR | BaseAddress | ) |

This function will wait until the I2C bus is free or timeout.

- Parameters

-

BaseAddress contains the base address of the I2C device.

- Returns

- XST_SUCCESS if the I2C bus was freed before the timeout.

- XST_FAILURE otherwise.

- Note

- None.

Definition at line 12 of file xiic_l.c.